# Vážení zákazníci,

dovolujeme si Vás upozornit, že na tuto ukázku knihy se vztahuje autorská práva, tzv. copyright.

To znamená, že ukázka má sloužit výhradně pro osobní potřebu potenciálního kupujícího (aby čtenář viděl, jakým způsobem je titul zpracován a mohl se také podle tohoto, jako jednoho z parametrů, rozhodnout, zda titul koupí či ne).

Z toho vyplývá, že není dovoleno tuto ukázku jakýmkoliv způsobem dále šířit, veřejně či neveřejně např. umisťováním na datová média, na jiné internetové stránky (ani prostřednictvím odkazů) apod.

# zajímavé aplikace kombinačních a sekvenčních logických obvodů

Tato kapitola seznamuje čtenáře s funkcí a použitím těchto logických obvodů: číslicový komparátor, multiplexer, demultiplexer, dekodér, budič sběrnice, řízený invertor, Schmittův klopný obvod. Dále jsou uvedena zapojení generátorů kmitů a budičů 7segmentových zobrazovačů.

## 4.1 ČÍSLICOVÉ KOMPARÁTORY

Komparátor je zařízení sloužící pro porovnání dvou veličin. Číslicovým komparátorem se pak rozumí logický obvod schopný porovnat hodnoty dvou jedno nebo vícebitových binárních čísel.

### 4.1.1 Komparátor na bázi hradla XOR

Nejjednodušším číslicovým komparátorem je prosté hradlo XOR. Z pravdivostní tab. 1.2 plyne, že pokud jsou hodnoty obou vstupů stejné, je výsledkem log. 0; v opačném případě je na výstupu log. 1. Někdy se také můžeme setkat s hradly XNOR. Ty mají oproti hradlům XOR výstup negovaný (při shodě je na výstupu log. 1, při rozdílu pak log. 0).

Pokud by bylo třeba porovnat dvě vícebitová čísla, musíme použít na každý bit jedno hradlo. Výstupy dílčích hradel XOR je třeba přivést na vstupy hradla OR, protože jedině tak bude výstup v log. 0, pokud jsou všechny vstupy v log. 0. Tedy při shodě obou vícebitových čísel je výstup hradla OR v log. 0, v opačném případě v log. 1<sup>1</sup>.

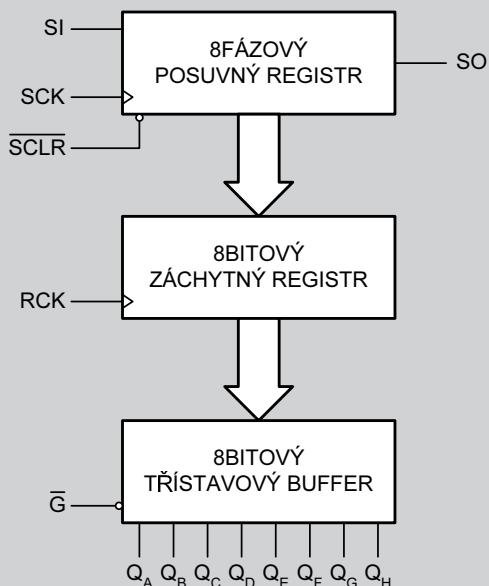

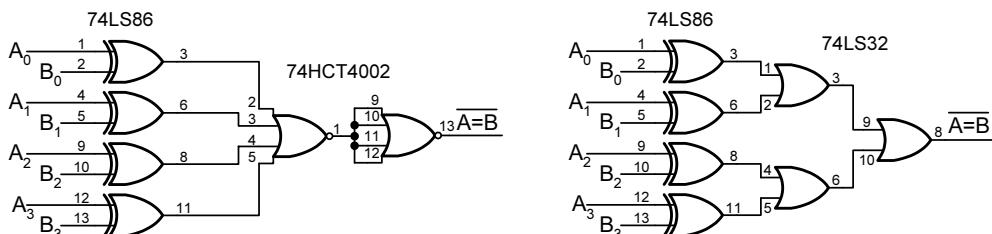

Obr. 4.1 ukazuje zapojení číslicového komparátoru pro 2 čtyřbitová čísla. Z výše uvedeného textu je jasné, že musí být použity čtyři hradla XOR (zde s výhodou použijeme obvod 74LS86, podrobný popis proveden v [1]) a dále 4vstupové hradlo OR (74HCT4002 obsahuje dvě 4vstupová hradla NOR; vstupy jsou přivedeny do prvního hradla a jeho výstup je znegován druhým hradlem). Druhá realizace používá tři 2vstupová hradla OR obsažená v obvodu 74LS32.

Obr. 4.1 Schéma zapojení 4bitového číslicového komparátoru s obvody 74LS86 a 74HCT4002 (napájení je u obou obvodů připojeno standardně: 14: 5 V a 7: 0 V)

<sup>1</sup> Pokud bychom používali hradla XNOR, musely by být dílčí výstupy podrobeny logickému součinu. Použili bychom tedy hradlo AND.

## 4.1.2 Komparátor 74LS688

Jak je z obr. 4.1 patrné, realizace číslicového komparátoru pro 4bitová čísla není příliš náročná (vystačíme se dvěma IO). V číslicové technice je velmi často třeba 8bitový číslicový komparátor. Jeho realizace podobným způsobem, jak ukazoval obr. 4.1, by byla příliš obtížná a nákladná. Bylo by zapotřebí 2 obvodů 74LS86 a dále obvod 74HCT4078 (8vstupové hradlo NOR), případně ještě invertor (například z obvodu 74LS04). Naštěstí jsou k dispozici 8bitové komparátory.

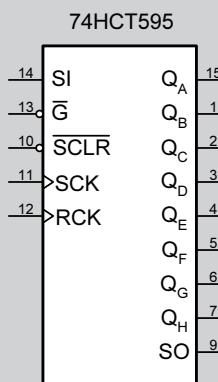

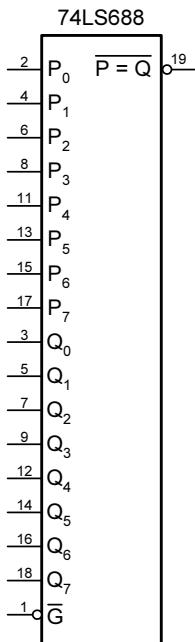

Obvod **74LS688** porovnává dvě 8bitová čísla. Bity prvního čísla přivádíme na vstupy  $P_0$  až  $P_7$ , druhé číslo pak na vstupy  $Q_0$  až  $Q_7$ . Jsou-li číselné hodnoty reprezentované bity obou čísel shodné, je výstup  $P = Q$  nastaven do log. 0. Pokud se čísla liší, je na výstupu log. 1. Vstup  $G$  je použitelný pro kaskádní řazení obvodů (tak lze například ze dvou obvodů 74LS688 vybudovat 16bitový adresový komparátor) nebo pro připojení nižší složky adresového dekodéru. Je-li,  $G = 1$  je výstup  $P = Q$  nastaven do log. 1 bez ohledu na stav ostatních vstupů. V opačném případě ( $G = 0$ ) je výstup  $P = Q$  nastaven do log. 1 pouze v tom případě, že se obě porovnávaná čísla liší. Rozložení vývodů ukazuje obr. 4.2.

Obr. 4.2

Rozložení vývodů číslicového komparátoru 74LS688

(napájení: 20: 5 V, 10: 0 V)

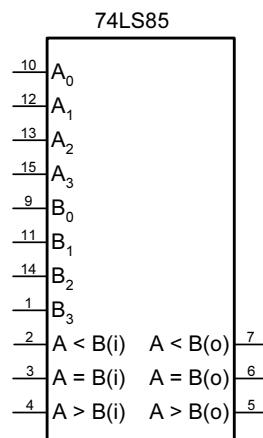

Obr. 4.3

Rozložení vývodů velikostního komparátoru 74LS85 (napájení:

16: 5 V, 8: 0 V)

Obvod 74LS688 nachází nejčastější použití jako *adresový dekodér*. Použití naleznete v kapitole 7.1.1.

### 4.1.3 Velikostní komparátor 74LS85

V kapitolách 4.1.1 a 4.1.2 byly zmíněny číslicové komparátory, které informují pouze o tom, zda se dvě čísla liší nebo zda jsou stejná. To je pro většinu aplikací naprosto postačující.

V případě, že je třeba čísla porovnat, můžeme použít obvod **74LS85**. Jedná se o 4bitový velikostní komparátor<sup>1</sup>. Obvod je vybaven vstupy pro kaskádní řazení, což nám umožňuje srovnávat čísla větší délky, pokud použijeme více těchto obvodů.

Vstupy  $A_0$  až  $A_3$  slouží k načtení hodnoty prvního čísla. Podobně vstupy  $B_0$  až  $B_3$  jsou určeny pro druhé číslo. Vstupy  $A < B(i)$ ,  $A = B(i)$  a  $A > B(i)$  jsou určeny pro kaskádní řazení. V tomto případě je připojíme na stejně označené výstupy obvodu v nižším řádu. Pokud obvod do kaskády nezapojujeme, musí být vstupy  $A < B(i)$  a  $A > B(i)$  připojeny na log. 0 a vstup  $A = B(i)$  zase na log. 1.

Výstupy  $A < B(o)$ ,  $A = B(o)$  a  $A > B(o)$  jsou aktivní v log. 1 a indikují příslušnou relaci obou porovnávaných čísel ( $A$  je menší než  $B$ ,  $A$  a  $B$  jsou shodná,  $A$  je větší než  $B$ )<sup>2</sup>.

Další informace o tomto obvodu jsou uvedeny v [1], použití viz kapitoly 4.8.2 a 7.1.1.

## 4.2 MULTIPLEXERY, DEMULTIPLEXERY A DEKODÉRY

*Multiplexer* je číslicový přepínač několika vstupů na jeden výstup. Takové obvody jsou tedy vybaveny vstupy, které se mají přepínat. Dále jsou zde adresové vstupy určující, který ze vstupů se má připojit na výstup. Dále mohou být doplněny vstupy pro odstavení obvodu (používají se pro kaskádní řazení). Tato skupina obvodů se někdy označuje jako *selektory dat*, což je vlastně jiný způsob popisu funkce těchto obvodů.

*Demultiplexer* funguje opačně než multiplexer. Z toho důvodu je vybaven větším počtem výstupů než vstupů. Vstupy mají význam adresy výstupu, který se má nastavit do log. 0, ostatní výstupy zůstanou ve stavu log. 1<sup>3</sup>.

Definice *dekodéru* bude složitější, protože pod tímto univerzálním označením se může skrývat mnoho obvodů. Jsou to například dekodéry umožňující zobrazení čísel pomocí 7segmentových zobrazovačů (7446, 7447; viz [1] a kapitolu 4.8) nebo pomocí digitronů (7441). Dále se používají dekodéry z binární formy na BCD kód. My se z této velké skupiny budeme věnovat pouze obvodům, jejichž použití je zajímavé ve spojení s mikroprocesorovou technikou (bude se jednat o dekodéry adresové).

<sup>1</sup> Velikostní komparátor znamená, že kromě obvyklého výstupu indikujícího shodu porovnávaných čísel, jsou zde ještě výstupy informující o tom, zda je první číslo větší nebo menší než druhé.

<sup>2</sup> Pokud je potřeba zkonstruovat složitější výraz, např.:  $A$  je větší nebo rovno  $B$ , použijeme výstupy  $A = B(i)$  a  $A > B(i)$  a přivedeme je na vstup logického hradla OR.

<sup>3</sup> Výjimečně se lze setkat s demultiplexery, které nastavují aktivní výstup do log. 1 a ostatní ponechají v log. 0.

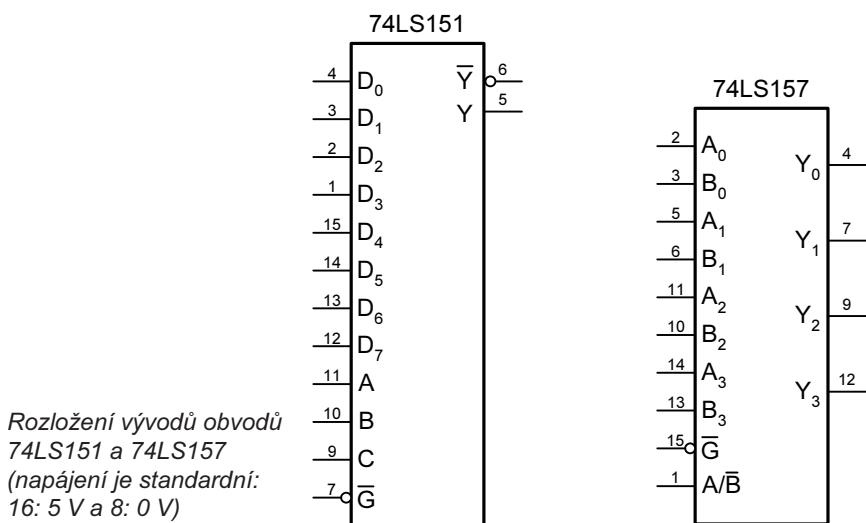

Obr. 4.4

Rozložení vývodů obvodů

74LS151 a 74LS157

(napájení je standardní:

16: 5 V a 8: 0 V)

#### 4.2.1 Multiplexer 74LS151 (8vstupový selektor dat)

Obvod **74LS151** je 8vstupový multiplexer (selektor dat). Protože 8 vstupů ( $D_0$  až  $D_7$ ) lze podle zákonů číslicové techniky adresovat 3 vstupy ( $8 = 2^3$ ), je obvod vybaven 3 adresovými vodiči (C, B, A). Dále je obvod vybaven vstupem kaskádního řazení  $G$  (aktivní v log. 0), který lze použít i pro vyřazení obvodu z činnosti. Výstupy dekódéru jsou dva – přímý a negovaný ( $Y$  a  $\bar{Y}$ ). Rozložení vývodů ukazuje obr. 4.4.

Popsat funkci obvodu pravdivostní tabulkou by bylo asi dosti složité a také obtížně pochopitelné. Proto dám přednost krátkému slovnímu vysvětlení: Je-li  $\bar{G} = 0$ , určuje číslo přivedené na adresové vstupy CBA (C je nejvyšší řad adresy) pořadové číslo vstupu, který bude „přepnut“ na výstup  $Y$  (na výstupu  $\bar{Y}$  se objeví jeho negace). Například pro  $CBA = 010$  (tj.  $3_{10}$ ) je přepnut vstup  $D_3$  na výstup. Je-li  $\bar{G} = 1$  je výstup  $Y = 0$ .

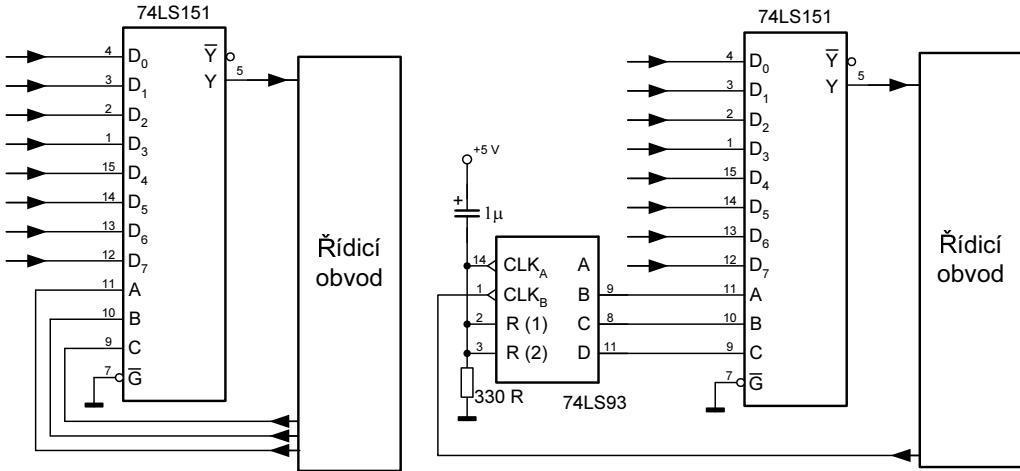

Multiplexery se obvykle používají v případě, kdy je třeba z nějakého důvodu „ušetřit“ propojovací vodiče. Máme-li například sledovat 8 vstupů, potřebujeme při klasickém řešení 8 vstupních vodičů. Pokud použijeme multiplexer, vystačíme s jediným vstupem, na který připojíme výstup multiplexeru. Vstupy multiplexeru pak postupně připojíme ke každému ze sledovaných vstupů. Jedinou komplikací je nutnost multiplexer adresovat, v tomto případě je třeba mít 3 výstupy, které připojíme na vstupy CBA, abychom zajistili adresování multiplexeru. Pokud je to pro nás velká komplikace, můžeme použít jiné řešení. Jak ukazuje obr. 4.5, lze pracovat s jediným výstupem, který má význam hodinového signálu čítače. Výstupy čítače pak připojíme na adresové vstupy multiplexeru. Z původně složitého propojení přes 8 vstupů, lze pomocí dvou integrovaných obvodů propojení „obsloužit“ jedním vstupem a jedním výstupem.

<sup>1</sup> Zajímavé použití přímého a negovaného výstupu by souviselo s přenosem signálu na velkou vzdálenost. V tomto případě je výhodné přenášet signál diferenciálně. Tedy ne zem a signál, ale signál a jeho negaci. Protože rušení působí na oba vodiče téměř stejně, může diferenciální vstup (odečítá oba signály od sebe) vliv rušení prakticky vynulovat!

Obr. 4.5 Sledování 8 vstupů multiplexerem. Vlevo klasické řešení s jedním vstupem a 3 výstupy, vpravo řešení s jedním vstupem a jedním výstupem

Rezistor s odporem  $330\ \Omega$  a kondenzátor s kapacitou  $1\ \mu F$  je použit pro počáteční vynulování čítače, aby bylo zajištěno, že výchozí adresa na vstupu CBA bude 000. Každá sestupná hrana hodin připojených na vstup CLK<sub>B</sub> způsobí zvýšení obsahu čítače o 1  $\Rightarrow$  přechod na další adresu. Po osmém impulu čítač automaticky přeteče, takže řídicí obvod může vstup ovzorkovat znovu, bez nutnosti opětovného vynulování čítače.

Bystřejší čtenáře s většími zkušenostmi patrně napadne, že pro realizaci tohoto typu zapojení (cyklické čtení několika vstupů pomocí jednoho vstupu a jednoho výstupu), by mohl být použit posuvný registr. Takové řešení jsme si také ukázali v kapitole 3.2 (obr. 3.20).

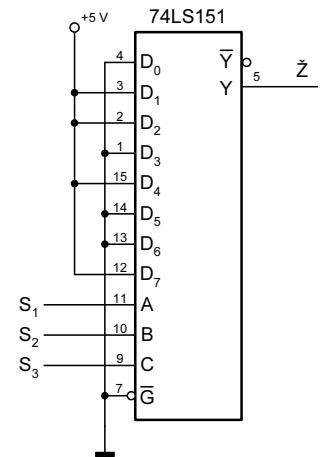

Zajímavým použitím multiplexeru je *realizace kombinační logické funkce přímo z pravdivostní tabulky* (stačí nám jeden obvod, minimalizace logické funkce se neprovádí). Jako ukázkou této možnosti řešme příklad 4 z kapitoly 1.10 použitím multiplexeru 74LS151. Viz obr. 4.6. Pro bleskovou orientaci je do tabulky připojen levý sloupec s desítkovým

| č. | C | B | A | Y |

|----|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 |

| 1  | 0 | 0 | 1 | 1 |

| 2  | 0 | 1 | 0 | 1 |

| 3  | 0 | 1 | 1 | 0 |

| 4  | 1 | 0 | 0 | 1 |

| 5  | 1 | 0 | 1 | 0 |

| 6  | 1 | 1 | 0 | 0 |

| 7  | 1 | 1 | 1 | 1 |

Obr. 4.6 Pravdivostní tabulka schodišťového spínače ovládaného ze 3 míst a schéma zapojení realizující tuto funkci multiplexerem 74LS151

vyjádřením hodnoty adresy na vstupech CBA. Realizace kombinační funkce je pak velmi jednoduchá. Pro řádky s log. 0 na výstupu je daný vstup připojen na log. 0. Pro řádky s log. 1 je připojen na log. 1. To je celé! Nevýhodou této realizace je obtížnější provedení v případě, že počet vstupů je vyšší než 3 (multiplexery s více než 8 vstupy jsou buď extrémně drahé nebo nejsou běžně v prodeji, případně se ani nevyrábějí).

## 4.2.2 Multiplexer 74LS157 (4 × 2vstupový selektor dat)

Obvod **74LS157** (rozložení vývodů viz obr. 4.4) je čtyřnásobným multiplexerem pro 2 vstupy. Je-li řídící signál  $G = 0$  a dále  $A/B = 1$  jsou na výstupy  $Y_0$  až  $Y_3$  připojeny vstupy  $A_0$  až  $A_3$ . Je-li řídící signál  $G = 0$  a  $A/B = 0$  jsou na výstupy  $Y_0$  až  $Y_3$  připojeny vstupy  $B_0$  až  $B_3$ . Je-li řídící signál  $G = 1$  jsou výstupy  $Y_0$  až  $Y_3$  v log. 0.

Z krátkého popisu je tedy zřejmé, že  $2 \times 4$  vstupy jsou na 4 výstupy připojovány současně. Zajímavou aplikací může být použití dvou obvodů 74LS157 například pro přepínání datové sběrnice o šíři 8 bitů<sup>1</sup>. V současnosti bude pro uvedené zapojení jednodušší použít dva osmibitové budiče sběrnice 74LS245 (viz kapitolu 4.3.2).

## 4.2.3 Dekodér 74LS138 (3bitový demultiplexer)

Obvod 74LS138 je 3bitový demultiplexer s negovanými výstupy. Vstupní adresa je přivedena na vodiče C, B, A. Pro normální funkci musí být řídící vstupy nastaveny takto:  $G_1 = 1$ ,  $\bar{G}_{2A} = 0$  a  $\bar{G}_{2B} = 0$ <sup>2</sup>. V tom případě je adresou CBA určeno, který z výstupů  $Y_0$  až  $Y_7$  je nastaven do log. 0 (číslo určené adresou udává číslo výstupu, který má být nastaven do log. 0), ostatní výstupy jsou nastaveny na log. 1. Obvod je tedy vhodný pro výběr obvodů, které sdílí část adresové sběrnice a mají být aktivovány log. 0, což je velmi častý případ (jmenujme například paměti).

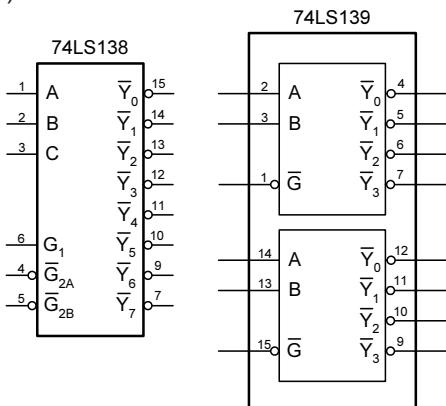

Obr. 4.7 Rozložení vývodů obvodů 74LS138 a 74LS139 (napájení je připojeno standardně: 16: 5 V a 8: 0 V)

<sup>1</sup> Tyto obvody byly podobně použity v legendárním, ale dnes již asi zapomenutém počítači ZX-Spectrum.

<sup>2</sup> V opačném případě jsou všechny výstupy v log. 1.

Pokud použijeme všechny řídicí vstupy, můžeme vedle sebe zapojit až 8 ( $2^3 = 8$ ) obvodů 74LS138.

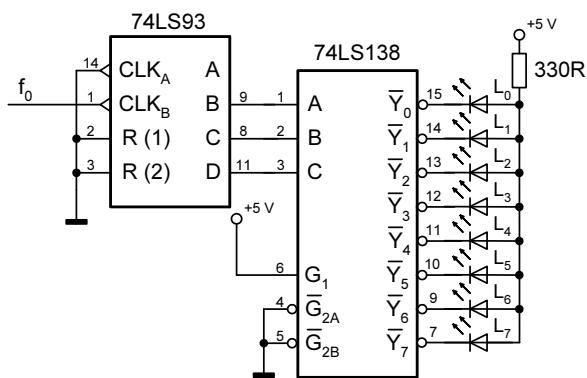

Obr. 4.8 ukazuje první z jednodušších aplikací obvodu 74LS138. Dekodér je zde použit pro výběr jedné z LED, která má svítit v zapojení běžně označovaném jako *běžící světlo*. Zde jsou řídicí vstupy nevyužity, tj. zapojeny standardním způsobem  $G_1 = 1$ ,  $G_{2A} = 0$  a  $G_{2B} = 0$ . Zajímavé je uvědomit si řešení připojení LED. Mělo by být zřejmé, že LED musí být připojeny katodou na výstup dekodéra a anodou na napětí 5 V (výstupy jsou aktivní v log. 0). Zajímavá je také skutečnost, že pro všechny LED stačí jeden omezovací rezistor, protože vždy svítí pouze jedna z celé osmice.

Obr. 4.8 „Běžící světlo“ s 3bitovým binárním čítačem a dekodérem 74LS138

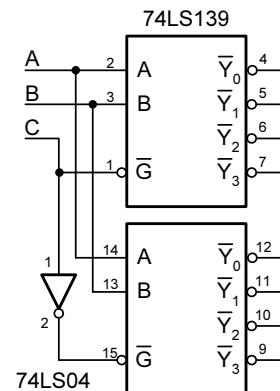

Obr. 4.9

Zapojení obou dekodérů obvodu 74LS139 vedle sebe

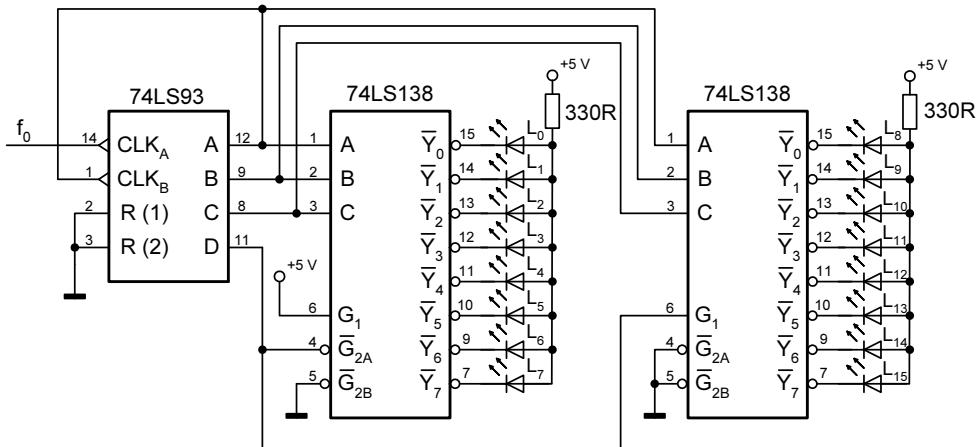

Obr. 4.10 ukazuje poněkud složitější aplikaci, kdy je *běžící světlo* sestaveno z 16 LED. Nyní je třeba použít dva obvody 74LS138, každý pro jednu osmici LED. Věnujme pozornost zapojení řídicích vodičů. Konvenční řešení by mohlo připojit 2 řídicí vstupy obou dekoderů běžným způsobem:  $G_{2A} = 0$  a  $G_{2B} = 0$ . Nezapojený řídicí vstup  $G_1$  by byl u prvního obvodu připojen přes invertor na výstup D čítače a u druhého dekodéru přímo. Takové řešení je správné, ale lze jej označit za hrubě konvenční. Hlavní nevýhodou je nutnost použít další IO obsahující invertor. Propojení vývodů dle obr. 4.10 je velmi promyšlené, obejdeme se bez invertoru. Základní myšlenka spočívá ve skutečnosti, že pro řešení prvního obvodu použijeme negovaný řídicí vstup a pro druhý přímý<sup>1</sup>. Samozřejmě, že i v tomto případě by mohlo být všech 16 LED napájeno z jediného rezistoru. V schématu jsem použil dva rezistory proto, abych nemusel kreslit další dlouhou čáru od jednoho dekodéru k druhému. Myslím si, že takto je schéma přehlednější.

<sup>1</sup> První obvod má být v akci pro výstupní kombinace čítače DCBA = 0000 až 0111, druhý pak pro DCBA = 1000 až 1111.

Obr. 4.10 „Běžící světlo“ pro 16 LED

#### 4.2.4 Dekodér 74LS139 (2 × 2bitový demultiplexer)

Obvod **74LS139** je svým chováním velmi podobný obvodu 74LS138. Jedná se vlastně o dva nezávislé 2bitové demultiplexery s negovanými výstupy. Pro načtení adresy slouží vstupy B a A. Při normální funkci musí být řídicí vstup G připojen na log. 0 (v opačném případě jsou všechny výstupy v log. 1). Adresa určená BA představuje číslo výstupu, který je nastaven do log. 0, ostatní výstupy jsou nastaveny na log. 1.

Pokud použijeme řídicí vstup G, můžeme vedle sebe zapojit oba demultiplexery z jednoho pouzdra. Takové schéma zapojení je na obr. 4.9. Horní dekodér je v akci pro řádově nižší adresy (CBA = 000 až 011), dolní pak pro řádově vyšší adresy (CBA = 100 až 111). Vše je umožněno použitím invertoru, který zajistí inverzi vstupu C pro dolní dekodér. Pro C = 0 je pak aktivován horní dekodér a pro C = 1 dolní.

### 4.3 OBVODY PRO PRÁCI SE SBĚRNICÍ

Číslicová technika nezavádí pojem „obvody pro práci se sběrnici“. Takto jsem si sám pro sebe označil obvody, které pracují s více vstupy a výstupy a každý podléhá stejné operaci. Jedná se o budiče sběrnice a vícenásobné klopné obvody D (ty byly probrány již v kapitole 2.1.8).

*Budič sběrnice* je obvod sloužící pro výkonové posílení logických signálů. Výkonové posílení je třeba jednak pro krytí špičkových odběrů při přepínání připojených obvodů (přechod z log. 0 na log. 1 či opačně), což je typické pro obvody na bázi unipolárních tranzistorů (řady CMOS 4000, HC, HCT), ale i pro vytvoření strmějších náběžných a sestupných hran (výkonější zdroj nabíhá rychleji).

Budič sběrnice může být konstruován jako jednosměrný (74LS244, 74LS240, 74LS241) nebo obousměrný (74LS245, 74LS640). Jednosměrný budič pouze výkonově posiluje vstupní signál, který může procházet jen v předem určeném směru. U obousměrného budiče je připojen další řídicí vstup, který určuje směr signálu.